Implementing the DN6678 CPU using an FPGA

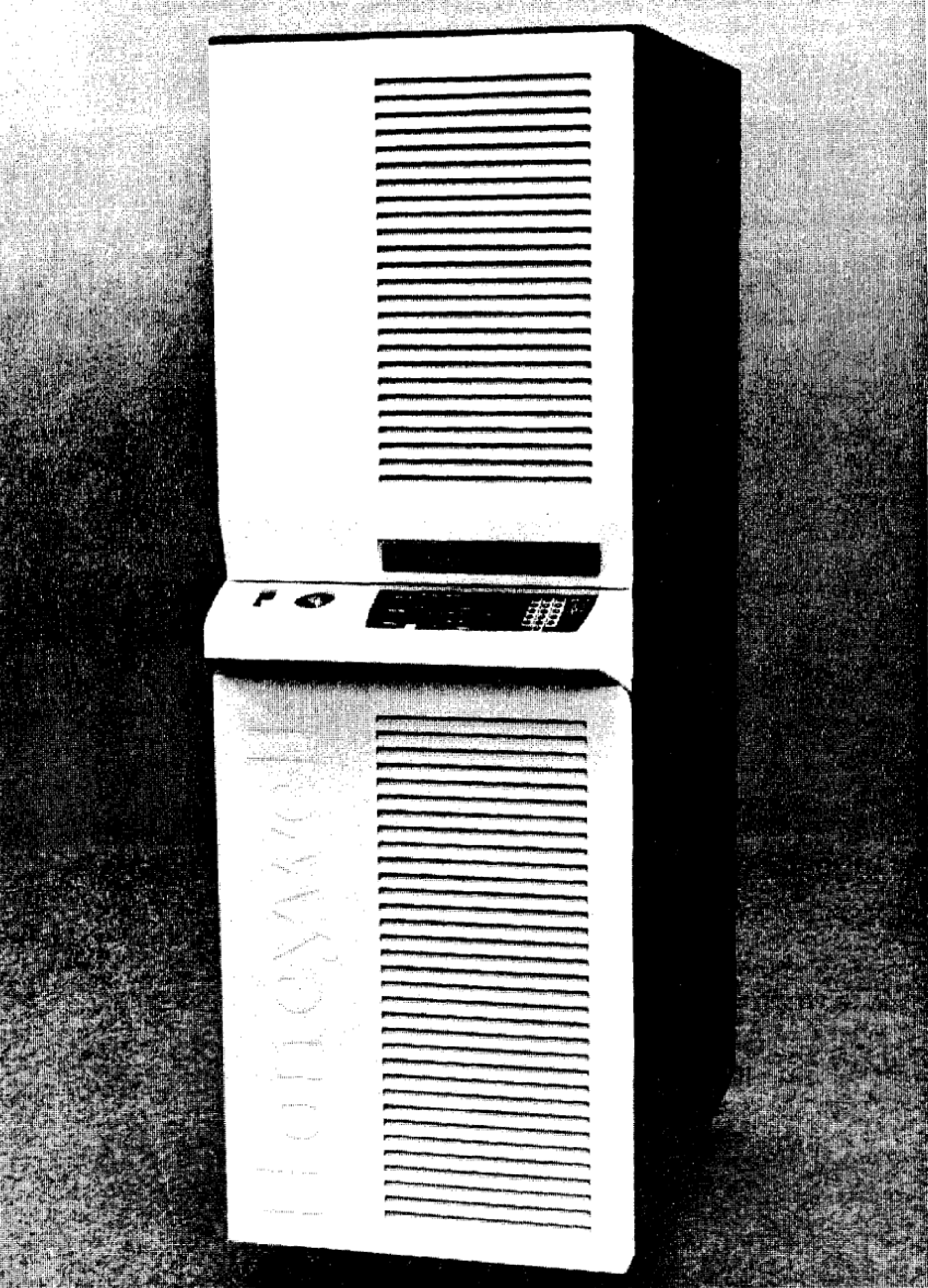

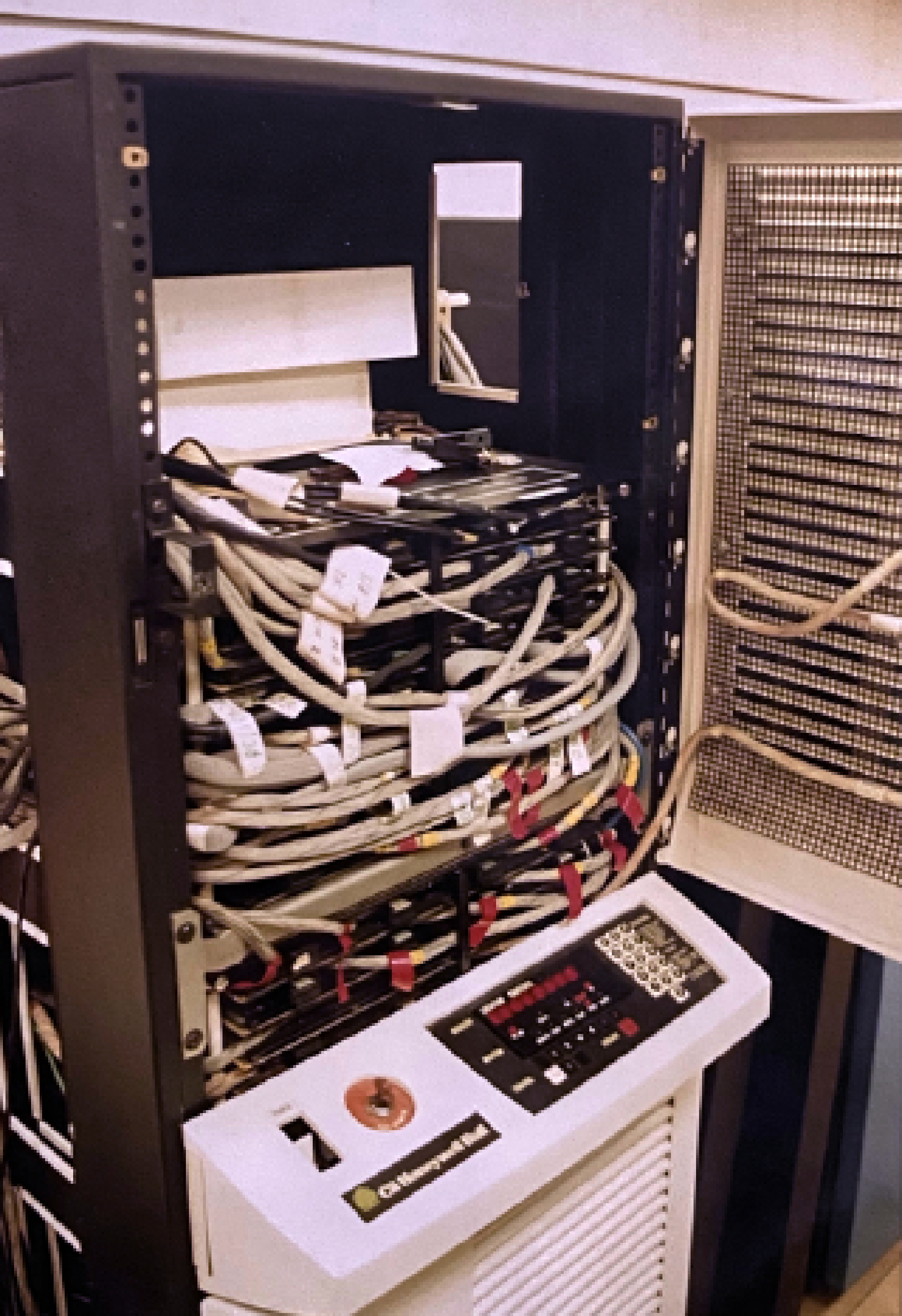

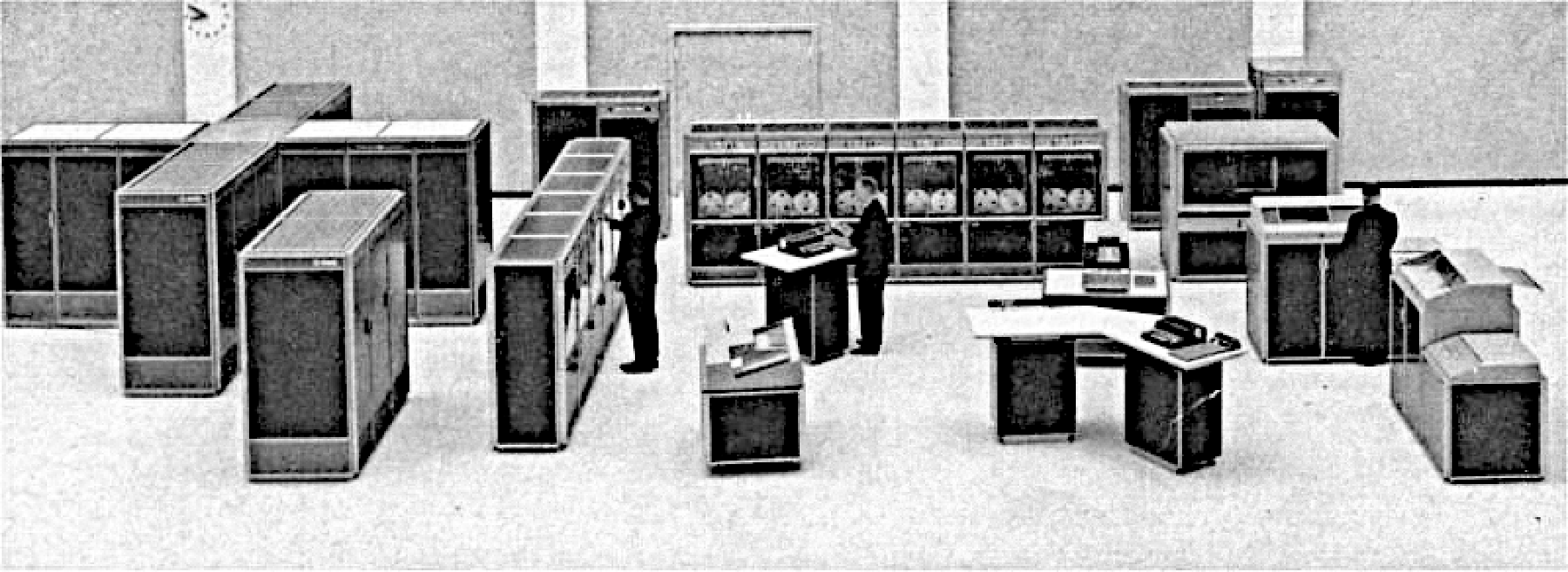

This post is going to discuss some of the specifics of the FPGA implementation of the Honeywell DATANET 6678 Front-End Network Processor.

First off, one of the main goals of this project, aside from achieving the end result, is to gain a thorough understanding of FPGA design and programming. To help accomplish this goal, I am reading the book “Computer Architecture Tutorial Using an FPGA” by Robert Dunne. This book provides excellent tutorials on FPGA programming using Verilog with the Terasic DE-10 Lite development board and offers a detailed guide on implementing a 32-bit ARM processor. I highly recommend this book.